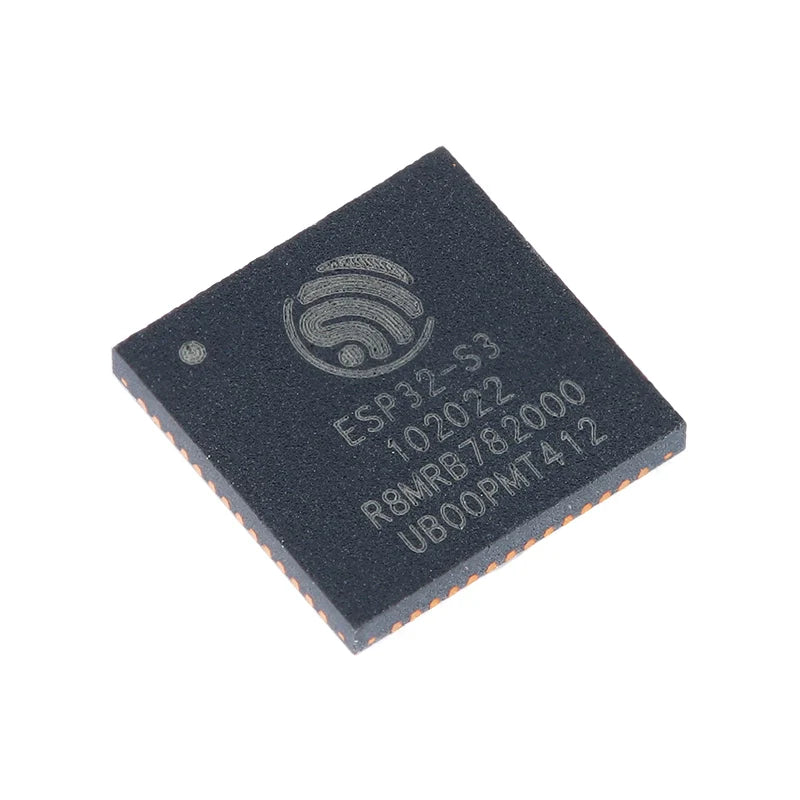

Original Genuine ESP32-S3R8 QFN-56 Wi-Fi+ Bluetooth 5.0 32-Bit Dual-Core MCU Chip 3.3V

Original Genuine ESP32-S3R8 QFN-56 Wi-Fi+ Bluetooth 5.0 32-Bit Dual-Core MCU Chip 3.3V

Regular price

¥15.80 CNY

Regular price

¥0.00 CNY

Sale price

¥15.80 CNY

Quantity

Couldn't load pickup availability

ESP32-S3R8/0FN-56

Product features

Wi-Fi

- Supports IEEE 802.11 b/g/n protocol

- It supports 20 MHz and 40 MHz bandwidths in the 2.4 GHz band

- Supports 1T1R mode with a data rate of up to 150 Mbps

- Wireless Multimedia (WMM)

- Frame aggregation (TX/RX A-MPDU, TX/RX A-MSDU)

- Immediate Block Acknowledgment (lmmediate Block ACK)

- Fragmentation and reorganization (the Fragmentation/defragmentation)

- Beacon Automatic Monitoring (Hardware TSF)

- 4x Virtual Wi-Fi interface

- It simultaneously supports the Station mode, SoftAP mode and hybrid mode of Station + SoftAP for basic infrastructure networks (lnfrastructure BSS)

- Please note that when ESP32-S3 is scanned in Station mode, the SoftAP channels will change simultaneously

- Antenna diversity

- 802.11mc FTM

- Supports external power amplifiers

Bluetooth

- Low-power Bluetooth (Bluetooth LE): Bluetooth 5,Bluetooth mesh

- High-power mode (20 dBm, sharing PA with Wi-Fi)

- The supported rates are 125 Kbps, 500 Kbps, 1 Mbps and 2Mbps

- Advertising Extensions

- Multiple Advertisement Sets

- 3 x UART

- 2 x I²C

- 2 x I²S

- 1 x RMT (TX/RX)

- 1 x pulse counter

- LED PWM controller, up to 8 channels

- 1 x Full-speed USB OTG

- 1 x USB Serial/JTAG controller

- 2 x MCPWM

- 1 x SDIO host interface, with 2 card slots

- Universal DMA Controller (abbreviated as GDMA), with 5 receiving channels and 5 transmitting channels

- 1 x TWA® controller, compatible with ISO11898-1(CAN Specification 2.0)

Analog interface

- 2 x 12-bit SAR ADC, up to 20 channels

- 1 x temperature sensor

- 14 x capacitive sensor GPIO

Timer

- 4 x 54-bit universal timer

- Channel Selection Algorithm #2

- Wi-Fi and Bluetooth coexist and share the same antenna

CPU and storage

- Xtensa® 32-bit LX7 dual-core processor, with a main frequency up to 240MHz

- CoreMark® score:

- Single core, main frequency 240 MHz: 613.86 CoreMark; 2.56 CoreMark/MHz

- Dual-core, main frequency 240 MHz: 1181.60 CoreMark; 4.92 CoreMark/MHz

- It has a 128-bit data bus bit width and supports SIMD instructions

- 384 KB ROM

- 512 KB SRAM

- 16 KB RTC SRAM

- The SPl, Dual SPl, Quad SPl, Octal SPl, QP, and OPI interfaces are externally connected to multiple fash and off-chip RAM

- An fash controller that introduces a cache mechanism

- Supports fash online programming

Advanced peripheral interfaces and sensors

- 45x GPIO port

- Digital interface:

- 4 x SPI

- 1 x LCD interface (8-bit to 16-bit parallel RGB,I8080,MOTO6800), supports mutual conversion between RGB565, YUV422, YUV420, and YUV411

-1 x DVP 8-bit to 16-bit camera interface

- 1 x 52-bit system timer

- 3 x watchdog timer

Low-power management

- Power management unit, five power consumption modes

- Low Power Coprocessor (ULP):

-ULP-RISC-V coprocessor

-ULP-FSM coprocessor

Security mechanism

- Safe startup

- Flash encryption

- 4096-bit OTP, with up to 1652 bits available to users

- Encryption Hardware accelerator:

- AES-128/256 (FIPS PUB 197)

- Hash (FIPS PUB 180-4)

- RSA

- Random Number Generator (RNG

-HMAC

- Digital signature

Comparison of ESP32-S3 series chips

| Order model | SiP flash | SiP PSRAM | Ambient temperature (°C) | SPI voltage |

| ESP32-S3 | - | - | - 40~ 105 | 3.3V / 1.8V |

| ESP32-S3FN8 | 8 MB (Quad SP) | - | - 40~ 85 | 3.3 V |

| ESP32-S3R2 | - | 2 MB (Quad SPl) | - 40~ 85 | 3.3 V |

| ESP32-S3R8 | - | 8 MB (Quad SPl) | - 40~65 | 3.3 V |

| ESP32-S3R8V | - | 8 MB (Quad SPl) | - 40~65 | 1.8 V |

Products photography